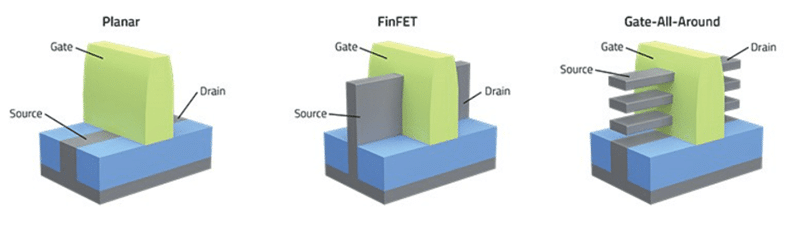

The semiconductor industry is making its first major changes to a new transistor type in more than a decade, moving toward the next generation of structures called ring gate (GAA) FET.

Although GAA transistors have yet to ship, many industry experts wonder how long the technology will be delivered — and what new architecture will take over from there. According to various roadmaps, barring major delays, today’s GAA structure should be implemented and expanded before the product’s three technical nodes are exhausted.

In addition, the industry is evaluating several transistor candidates, each with technical gaps. Even developing a product candidate to successfully extend CMOS FET by a decade will require significant resources and innovation.

In the short term, however, there is a clear path for the industry to migrate to the highest performance chips. Traditionally, to advance new chips, IC vendors develop a system-on-chip (SoC) and cram more transistors into each generation of devices. Transistors are a key component of chips, acting like switches in devices.

This formula is called chip scaling, and each chip costs roughly the same as long as the industry can develop new, faster transistors that consume the same or less power. Since 2011, suppliers have been shipping chips based on an advanced transistor type called finFET. However, finFET will soon be approaching its limits, prompting the need for new technologies for 3nm and/or 2nm process nodes. Nodes refer to performance specifications, process techniques, and design rules for a generation of technologies. Process techniques are formulations used to make chips in a wafer fab. The chip industry began to refer to nodes above 2nm as angstrom nodes.)

At 2nm and/or 3nm, leading founders and their customers will eventually migrate to GAA transistor types called nanosheet FET. GAA FETs provide higher performance at lower power than FINFets, but they are more expensive to design and manufacture.

Engineers know that even today’s GAA designs will eventually encounter performance limitations. The industry is planning ahead by evaluating several future transistor types beyond 2nm, including 2D devices, carbon nanotube FETs, CFEts, fork-plate FeTs, and vertical transport FeTs. So far, there is little consensus on 2nm.

While these novel structures can provide amazing electrical properties, they are difficult to manufacture. As a result, most people never move from a lab to a fab. In practice, the industry can only support one transistor candidate.

This is not the only consideration. “[We have] new transistor architectures,” Said Chung Hoon Lin, Intel’s senior director and principal engineer, in a speech at the recent IEDM conference. “In addition to the transistor side of the technology, there are also new architectures involved, such as new power transmission systems. Then there is packaging, which is very popular and important.”

In fact, as an advanced form of packaging, small chips have caused a stir for a number of reasons. Using small chips, bare-chip designs are broken down into smaller bare-chip pieces that, once manufactured and segmented, are reassembled into an advanced package. The small chip approach speeds time-to-market, increases production, and may reduce costs. As spacing scaling becomes more difficult and expensive, stacked small chip designs become a compelling solution for specific high-performance applications.

In short, a holistic approach to optimizing performance from transistors to systems becomes necessary to maintain the pace of performance in the industry.

Transistor problem

The IC industry has followed the same basic formula for decades. Every 18 to 24 months, chip makers come out with a new process technology with higher transistor density, thereby lowering the cost per transistor. At each node, chip makers have expanded transistor specifications by 0.7 times, enabling the industry to deliver a 40 percent performance increase and a 50 percent area reduction for the same amount of power. Chip scaling fuels most of our new electronics, which perform more and more functions at higher speeds with less energy.

Using flat transistors, the semiconductor industry advances various process nodes at each technology node using advanced lithography tools and other process enhancements. Then around 2011, when flat transistors suffered from short channel effects, the industry hit a snag with 20nm technology. “For example, the current can leak between the source and the drain even when the flow should be turned off,” said Nerissa Draeger, project director at Lam Research University.

Flat transistors are still optimized for chips at 22nm and above, but the industry needs a new solution. Intel began manufacturing finFET transistors at 22nm nodes in 2011. The foundry was later moved to 16nm/14nm finFET.

FinFET has several advantages over planar transistors. “Compared to previous flat transistors, fins with gates touching on three sides give better control over the channels formed within the fins,” Draeger said.

Using a variety of process steps in fabs, chip manufacturers have shrunk and extended finFET to 7nm and 5nm to enable new high-performance chips.

However, many chips do not require finFET. Digital chips and analog, rf, and other devices still use flat transistors. They are all thriving. For example, 28nm flat products remain one of the largest markets by node.

Umc’s 28nm technology revenue, for example, rose 75 percent in the most recent quarter. “The 75 per cent year-on-year revenue growth reflects strong chip demand related to 5G, the Internet of things and vehicles,” said Jason Wang, umC’s co-president.

At the forefront, meanwhile, chip miniaturization presents special challenges. At 7nm and below, static leakage becomes an issue and the power and performance advantages begin to diminish. Currently, performance improvements are in the 15 to 20 percent range.

When the finFET’s fin width reaches 5nm (near the 3nm node), the contact polycrystalline silicon spacing (CPP) reaches a limit of about 45nm and the metal spacing is 22nm. CPP is the distance separating the centers of adjacent gate contacts.

Still, the industry needs faster chips above 5nm. “Even now, we can use 10 times more computing power,” says Aki Fujimura, CHIEF executive of D2S. “Heavy simulation such as weather forecasting, bitcoin mining or deep learning is driving demand for 3nm and above. Fortunately, we will continue to scale, even though Moore’s Law is changing.”

Coming soon: GAA FEts, Chiplets

Today, Intel, Samsung and TSMC are developing the 3nm process, and several companies are using it to develop chips.

It is an expensive endeavour. “The average cost of designing a 28nm chip is $40 million,” said Handel Jones, CEO of IBS. “By comparison, it cost $217 million to design a 7nm chip and $416 million to design a 5nm device. The 3nm design will cost up to $590 million.”

In addition, contract customers face tough choices at 3NM. Unlike previous nodes, chipmakers follow the same transistor path, and contract suppliers are developing different 3nm technologies. Samsung plans to move from finFET at 5nm nodes to GAA at 3nm nodes. In contrast, Intel and TSMC plan to extend finFET at 3nm and then move to GAA at 2nm.

Samsung, by contrast, wants to compete in the GAA era. The company announced an early version of the 3nm GAA in 2022, with a “performance version” shipping in 2023.

This will put Samsung ahead of the competition. “TSMC is most likely to have a GAA-BASED 2nm, targeting production in 2025. Intel’s 20A process, or 2nm, is GAA. It is planned to be launched in 2024, “Wang said.

All leading chipmakers are developing a popular GAA transistor, the Nanosheet FET (Intel calls it RibbonFET). The nanosheet FET is a finFET that is rotated 90 degrees to produce horizontally stacked fins with vertical gate material in the middle for each fin. Each fin is like a piece of paper, a passage.

On the surface, the miniaturization advantage between 3nm finFET and nanosheets seems small. According to analyst estimates, both provide 48nm CPP with 22nm metal spacing.

Nevertheless, the nanosheet structure has significant advantages. “A Gate-all-around or GAA transistor is an improved transistor structure in which the Gate touches the channel from all sides and achieves continuous scaling,” Lam’s Draeger explains. “This provides improved channel control over finFET.”

In contrast, with finFET, the width of the device is quantified. In nanosheets, designers can change the width of the sheet. Wider plates provide more drive current and performance. The narrower nanosheet has a smaller driving current but occupies a smaller area.

A disadvantage of nanosheets is the low performance of pFET due to low hole mobility in silicon-based channels.

One solution to this problem described by IBM in the IEDM is a pFET using a compressed strain silicon-germanium (SiGe) channel material. “The nanosheet pFET SiGe channel provides a 40% mobility increase and a 10% performance gain over the silicon channel, while reducing threshold voltage (Vt) and improving negative bias temperature instability (NBTI),” said Ruqiang Bao, SENIOR Engineering Manager, IBM.

Fabrication of nanosheet FETs presents significant challenges. In the process, epitaxial tools deposit ultra-thin, alternating layers of SiGe and silicon on the substrate to form a superlattice structure. Such structures may have three, five, or more layers of each material.

Tiny vertical fins are patterned and etched in a superlattice structure. Then, the inner spacer is formed. In interval etching, the outer portion of the SiGe layer in the superlattice structure is depressed and then filled with a dielectric material.

Next, the source/drain is formed. The SiGe layer in the superlattice structure is then removed, leaving behind the silicon substrate or sheet that forms the channel. Finally, the gate is formed by deposition of high K dielectric and metal gate material.

Every step is a challenge. As with all processes, the goal is to develop a chip without defects. This requires the adoption of a sound process control strategy in the fab.

“Process control at smaller nodes is more challenging,” says Julie Ply, Director of Quality materials at Brewer Science. “There are several reasons for this: 1) the detection limit must be continually lowered to detect meaningful signals in smaller nodes; 2) Process signals may need to be further refined and reduced to provide a higher level of control; 3) The value of materials at smaller nodes generally increases, making early detection and correction more important than ever to mitigate potential losses.”

At 3nm and beyond, the industry will need new innovations and fabs. Among them are:

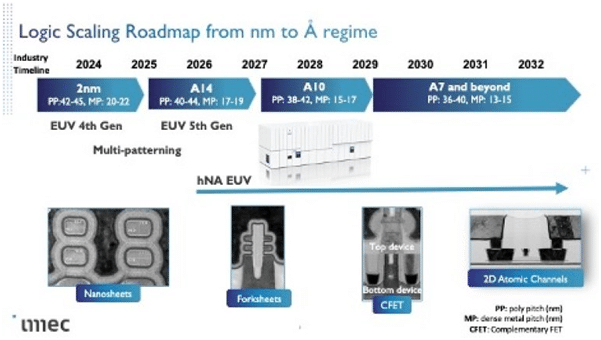

- Cathodic ultraviolet (EUV) lithography. Using 13.5nm wavelengths, EUV has been used to pattern tiny features at 7nm and 5nm. The next generation of high-na EUV is under development and requires patterning of finer features above 3nm:

- Atomic processing at the atomic level. Atomic layer deposition (ALD) and the next generation of etching techniques are required to deposit and etch materials in structures.

- Cost check and metrology. New methods are needed to find defects and measure them.

Transistor manufacturing is only one part of the solution for a 3nm system. Chip design is critical. On-chip interconnection, assembly, and packaging must minimize the impact on device and system performance.

At IEDM, Imec proposed a solution to this problem — 3D SoC. In one example, Imec designed a 3D design with 256 cores. But advanced design capabilities are necessary. “This requires dedicated EDA tools that can handle both designs simultaneously, using automated tools for system partitioning and 3D critical path optimization during layout and routing, which takes small chips to a new level,” said Dragomir Milojevic, CHIEF scientist at Imec.

The future choice

Chiplet technology continues to evolve, while transistor expansion slows. Barring any delays, nanosheet FET is expected to perform well in three technology generations, from 3nm nodes in 2022 to 2nm in 2025 and 1.5nm in 2028, according to the International Equipment and Systems Roadmap (IRDS).

In an IEDM paper, TEL Outlines a possible scaling path for nanosheets. According to TEL, the first-generation nanosheet FET can be composed of three nanosheets, each 30nm wide. The device uses 48nm CPP and 22nm metal spacing.

Then, by scaling the device to 0.73X, the second generation of 4-chip FETs can be modified by = >; 46 nm CPP and = & gt; The 18-nm metal spacing consists of the company said. Third-generation devices can magnify these dimensions by 0.78 times.

According to IRDS, by 2031, nanosheet FETs may no longer provide the desired performance at low power consumption and cost. The roadmap is expected to shift to new transistors – complementary FET (CFET) around 1nm nodes.

Imec’s roadmap tells a slightly different story. The institute plans to expand the nanosheet to 2027, followed by the introduction of forked FET. Then, CFET will appear around 2029.

Through design and process optimization, the nanosheet may extend longer than expected, eliminating the need for splicing, CFET, or other candidate materials. In fact, nanosheet FETs may be the last type of transistor.

Nevertheless, fork plates and CFETS show great potential. Both technologies are different from existing GAAS, which use different devices for nFET and pFET.

Imec researchers are the innovators behind Forksheet FET, which has two nanosheet FET adjacent to each other on a single device. One nanosheet FET (three pieces) was composed of pFET, while the other nanosheet (three pieces) was composed of nFET. The dielectric wall separates nFET from pFET.

“You can extend the N to P space between NMOS devices and PMOS devices in standard cells to create greater active device widths,” said Sri Samavedam, senior vice president of CMOS technology at Imec. “It gives you a much larger effective width in the same occupying area compared to nanosheets, and it also has a lower parasitic capacitance, with a performance advantage of about 10 percent compared to nanosheets.”

Recently, Intel published a paper on CFETS with 13nm wide sheets and 9nm spacing between each sheet. “This method combines excellent static electricity with a way to significantly reduce cell size,” says Intel’s CY Huang.

CFET has two different processes, monolithic and sequential. Both are complex, and not all processes and tools are commercially available today. They require a lot of money to develop.

The monolithic approach involves more complex CMOS processes. “The monolithic CFET approach involves building NMOS and PMOS devices on the same chip,” says Samavedam of Imec. “The active region and gate of both devices are self-aligned. The process requires several high aspect ratio processing steps, such as deposition and etching. This requires development.”

In the sequential approach, NMOS and PMOS transistors are processed on separate chips and then bonded. “With the sequential CFET approach, NMOS and PMOS devices can be formed on separate wafers so that they can be individually optimized, as if with different channel materials or substrate orientations,” Samavedam said. “The challenge is that the active region and gate are not self-aligned. It requires high-precision top and bottom wafer alignment and bonding, as well as novel integration to connect the top and bottom device grids. Since each device is built separately, sequential CFETS require additional processing steps.”

Distant future choices

For many years, the industry has been researching two-dimensional material FETs. These devices are still in the development stage and could appear after 2030, once they become commercially viable.

2D FET is similar to nanosheet FET. The biggest difference is that the channels are based on transition metal disulfide (TMD) materials, such as molybdenum disulfide (MoS 2), selenite tungsten (WSe 2) and others. TMD enables thinner channels for gate length scaling and high channel mobility.

On the IEDM, Intel describes a variety of 2D FETs, including nanoribbon FETs with a 5nm gate length. In another example, Intel describes a PMOS device that uses a WSe 2 thin film to achieve a 141mV/ Dec subthreshold swing.

Samavedam of Imec talked about the challenges facing 2D FETS. “These materials still have a number of fundamental material issues to solve, such as defect reduction, variability, improved channel mobility, formation of low resistance contacts, doping, and formation of scaled gate dielectrics.”

About Electronic components distributor FAST TURN CHIP

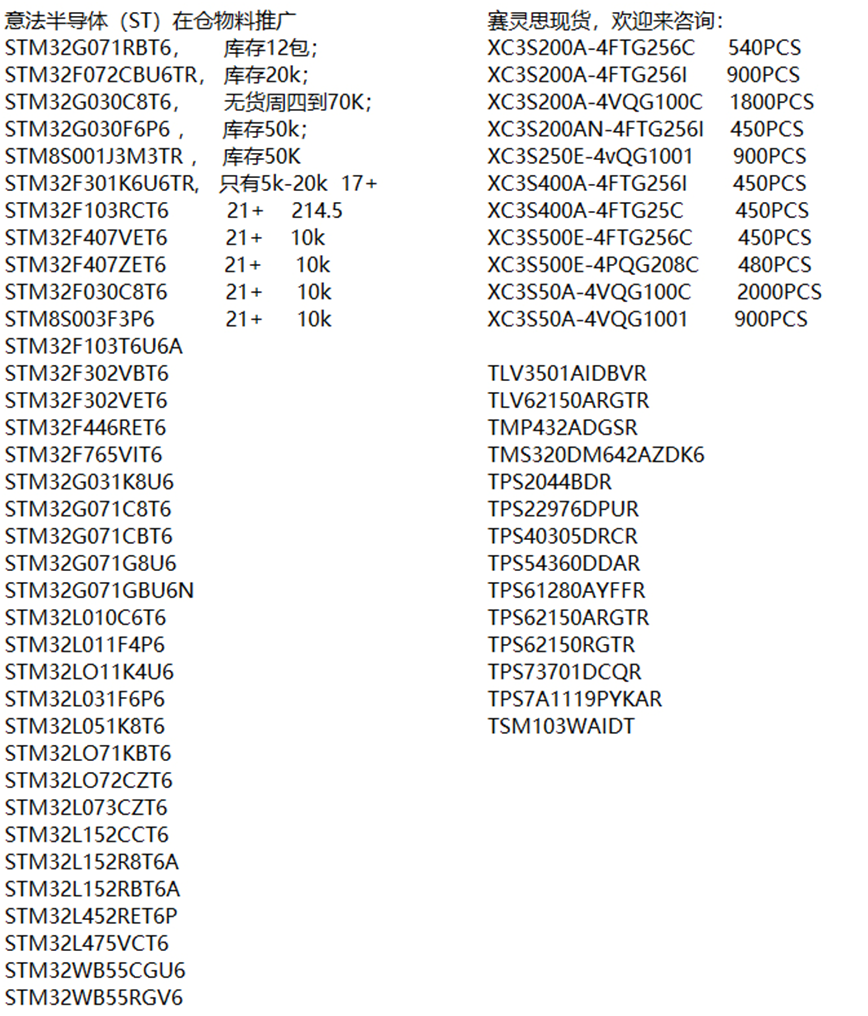

FAST TURN CHIP is a B2B electronic contract manufacturer, with a number of electronic components procurement points. We can find and purchase hybrid electronic components and ics at competitive prices to meet customer needs. No matter what components you want, no matter how many, you can buy from Cocreate At a reasonable price and with traceable quality.

ST Spot stock :

For quotation please contact: Miss Huang 15018735409

Company website: https://fastturnchip.cn/